#### Jori Lemettinen

# Epitaxy of gallium nitride films on silicon substrates

#### **School of Electrical Engineering**

Thesis submitted for examination for the degree of Master of Science in Technology.

Espoo 3.8.2015

Assignment supervisor:

Prof. Markku Sopanen

Assignment advisor:

D.Sc (Tech.) Sami Suihkonen

Author: Jori Lemettinen

Title: Epitaxy of gallium nitride films on silicon substrates

Date: 3.8.2015 Language: English Number of pages: 7+48

Department of Micro and Nanosciences

Professorship: Optoelectonics Code: S-104

Supervisor: Prof. Markku Sopanen

Advisor: D.Sc (Tech.) Sami Suihkonen

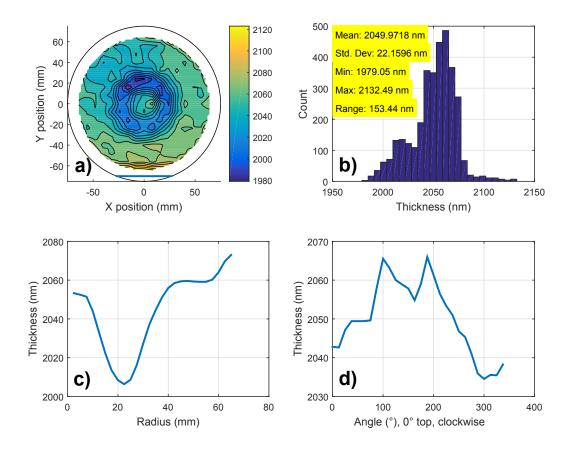

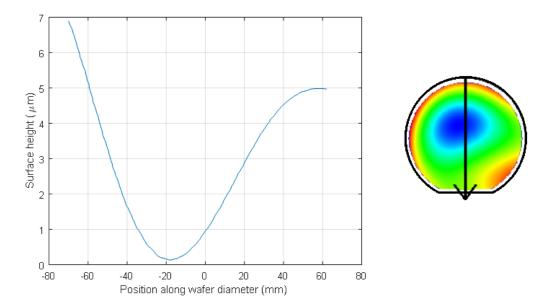

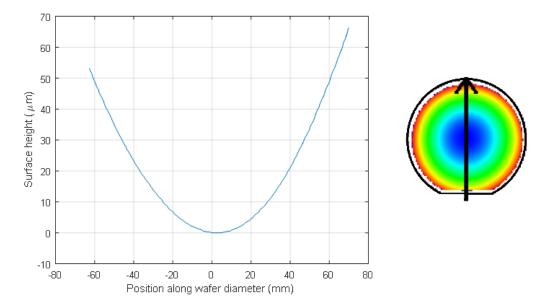

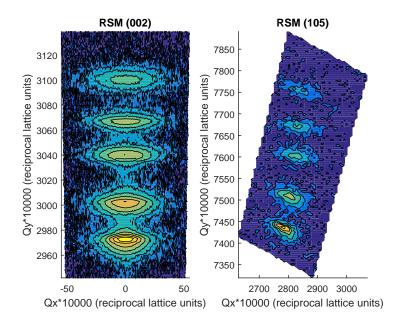

Metal organic vapour phase epitaxy (MOVPE) of c-plane gallium nitride (GaN) on 6-inch (111) silicon substrates is studied in this thesis. GaN layers were grown by an Aixtron 6" CSS MOVPE employing an aluminium nitride nucleation layer and a step graded aluminium gallium nitride buffer layer. The epitaxial layer thicknesses were mapped over the whole wafer with a spectrophotometer. The total film thickness was approximately 2.05  $\mu$ m. The thickness uniformity was good and the standard deviation was 1.1% (10 mm edge exclusion). The wafer geometry was measured using capacitive profiling. The wafer bow was 80.1  $\mu$ m after growth. The bow was non-spherical probably due to thickness non-uniformity. Reciprocal space maps around (002) and (105) reflections were measured with x-ray diffraction. The GaN layers were under tensile strain at room temperature. The full width at half maximum of the (002) and (105)  $\omega$ -scans were 800 and 770 arcsec, respectively. To further improve the structure a thicker buffer layer possibly with higher aluminium content should be used to reduce wafer bow. Also dislocation reduction techniques such as  $SiN_x$  interlayers should be considered to increase crystal quality. In addition, aluminium predose instead of nitridation could be employed.

Keywords: gallium nitride, metal-organic vapour phase epitaxy

Tekijä: Jori Lemettinen

Työn nimi: Galliumnitridin epitaksia piialustakiteille

Päivämäärä: 3.8.2015 Kieli: Englanti Sivumäärä: 7+48

Mikro- ja nanotekniikan laitos

Professuuri: Optoelektroniikka Koodi: S-104

Valvoja: Prof. Markku Sopanen

Ohjaaja: TkT Sami Suihkonen

Tässä diplomityössä tutkitaan c-kidetason galliumnitridin (GaN) valmistusta metallo-organisella kaasufaasiepitaksialla (MOVPE) 6:n tuuman (111)piialustakiteille. GaN-kerrokset valmistettiin Aixtron 6" CCS MOVPE -laitteella käyttäen alumiinintridiydintymiskerrosta ja porrastettua alumiinigalliumnitridipuskurikerrosta. Valmistettujen kerroksien paksuus mitattiin koko kiekon alueelta valkoisen valon heijastusmittauksella. Valmistettujen kerrosten yhteinen paksuus oli noin 2,05  $\mu$ m ja kerrospaksuuden keskihajonta oli 1,1% (tuloksesta poistettu 10 mm kiekon ulkoreunalta lukien). Kiekon geometria mitattiin kapasitiivisella profiloinnilla ja havaittiin, että kiekon kaarevuus oli 80,1  $\mu$ m. Kaarevuus ei ollut täysin ympyräsymmetrinen johtuen todennäköisesti valmistetun kerroksen paksuusvaihtelusta. Röntgendiffraktiolla mitattiin (002)- ja (105)heijastuksista käänteishilakartat, joiden perusteella GaN-kerrokset olivat vetojännitystilassa huoneenlämmössä. Puoliarvoleveydet (002)- ja (105)-heijastuksille olivat 800 ja 770 kaarisekuntia. Rakennetta voitaisiin parantaa käyttämällä paksumpaa puskurikerrosta tai lisäämällä alumiinin määrää kerroksissa. Kidevirheiden määrää pitäisi pienentää esimerkiksi käyttämällä piinitridivälikerroksia. Prosessi voitaisiin myös aloittaa atomaarisella alumiinipäällystyksellä pinnan nitrauksen sijaan.

Avainsanat: Galliumnitridi, metallo-organinen kaasufaasiepitaksia

# **Preface**

This Master's thesis was conducted at the Aalto University, School of Electrical Engineering, Department of Micro- and Nanosciences, Optoelectronics research group. I would like to thank Professor Markku Sopanen for the opportunity to write my thesis on this exciting topic. I wish to thank my advisor D.Sc Sami Suihkonen for interesting discussions on all things scientific and general, expertise, help and guidance during this work. I wish to thank D.Sc Atte Haapalinna and Okmetic Oyj for providing high quality silicon substrates vital for this study and for organising the wafer geometry measurements.

I want to thank M.Sc Christoffer Kauppinen for his help in characterization. I wish to thank all the personnel of the Micro- and Nanosciences department for the friendly and pleasant working environment. In addition, I cannot stress enough the importance of free coffee available in the 4th floor kitchen.

Finally, I want to thank my family and friends, especially my parents, for all the support and for letting me dismantle most of our household appliances.

Otaniemi, 29.7.2015

Jori A. Lemettinen

# Contents

| $\mathbf{A}$ | bstra                      | act                        | ii           |  |  |  |  |

|--------------|----------------------------|----------------------------|--------------|--|--|--|--|

| <b>A</b>     | bstra                      | act (in Finnish)           | iii          |  |  |  |  |

| Pı           | refac                      | e                          | iv           |  |  |  |  |

| C            | onter                      | nts                        | $\mathbf{v}$ |  |  |  |  |

| $\mathbf{A}$ | bbre                       | viations                   | vii          |  |  |  |  |

| 1            | Intr                       | roduction                  | 1            |  |  |  |  |

| 2            | Crystalline semiconductors |                            |              |  |  |  |  |

| _            | 2.1                        | Crystal lattice            | <b>3</b>     |  |  |  |  |

|              | 2.2                        | Semiconductors             |              |  |  |  |  |

|              | $\frac{2.2}{2.3}$          | Compound semiconductors    |              |  |  |  |  |

|              | 2.4                        | Gallium nitride            |              |  |  |  |  |

| 3            | MO                         | OVPE                       | 11           |  |  |  |  |

|              | 3.1                        | Operation                  | 11           |  |  |  |  |

|              | 3.2                        | Growth mode                |              |  |  |  |  |

|              | 3.3                        | Growth regime              | 14           |  |  |  |  |

|              | 3.4                        | Growth of GaN              |              |  |  |  |  |

|              | 3.5                        | Substrates for GaN epitaxy | 16           |  |  |  |  |

| 4            | Aixtron 1x6" CCS MOVPE     |                            |              |  |  |  |  |

|              | 4.1                        | System                     | 19           |  |  |  |  |

|              | 4.2                        | In situ monitoring         | 20           |  |  |  |  |

| 5            | Cha                        | Characterization methods   |              |  |  |  |  |

|              | 5.1                        | Spectrophotometer          | 25           |  |  |  |  |

|              | 5.2                        | X-ray diffraction          |              |  |  |  |  |

|              | 5.3                        | Wafer geometry measurement | 29           |  |  |  |  |

| 6            | Gallium nitride on silicon |                            |              |  |  |  |  |

|              | 6.1                        | Substrate orientation      | 30           |  |  |  |  |

|              | 6.2                        | Buffer layers              | 31           |  |  |  |  |

|              | 6.3                        | Wafer bending              | 31           |  |  |  |  |

|              | 6.4                        | Crystal quality            | 33           |  |  |  |  |

| 7            | Results                    |                            |              |  |  |  |  |

|              | 7.1                        | Optimizing growth          | 34           |  |  |  |  |

|              | 7.2                        | Growth process             | 36           |  |  |  |  |

|              | 7.3                        | Layer thickness            | 38           |  |  |  |  |

|              | 7.4                        | Wafer geometry             | 40           |  |  |  |  |

|            |                       | vi |  |

|------------|-----------------------|----|--|

|            | 7.5 X-ray diffraction | 41 |  |

| 8          | Conclusion            | 44 |  |

| References |                       |    |  |

#### Abbreviations

2D two-dimensional 3D three-dimensional

Al aluminium

AlGaN aluminium gallium arsenide

AlN aluminium nitride CCD charge-coupled device CCS close coupled showerhead

CMOS complementary metal oxide semiconductor

ELOG epitaxial layer overgrowth

FET field effect transistor

FM Frank-van der Merwe

FWHM full width at half maximum

Ga gallium

GaAs gallium arsenide

GaAsP gallium arsenide phosphide

GaN gallium nitride

HEMT high electron mobility transistor HRXRD high resolution x-ray diffraction HVPE hydride vapour phase epitaxy

InN indium nitride InP indium phosphide

LD laser diode

LED light emitting diode MBE molecular beam epitaxy

MEMS micro electro mechanical system

Mg magnesium

MOVPE metal organic vapour phase epitaxy

N nitrogen

RSM reciprocal space map

Si silicon

SiC silicon carbide

SK Stranski-Krastanov

TEGa triethylgallium

TMAl Trimethylaluminum

TMGa Trimethylgallium

TMIn Trimethylaluminum

UV ultraviolet VW Volmer-Weber XRD x-ray diffraction

# 1 Introduction

Gallium nitride (GaN) is a compound semiconductor that belongs to the nitride subset of III-V compound semiconductors. GaN has become the second most important semiconductor after silicon (Si) [1]. The electrical and physical properties, such as the direct and wide bandgap in addition to good thermal and chemical stability, make GaN a highly interesting material [2].

The direct bandgap allows efficient optoelectronic applications. GaN based blue light emitting diodes (LED) have received attention [3]. Blue LEDs can be, in turn, used to create white LEDs. This is done by converting some of the emission to longer wavelengths, usually by using different phosphorous coatings [3]. The result is a LED whose emission resembles white light. An efficient while light source can reduce the energy consumption of lighting tremendously. In fact, the GaN based white LEDs have seen increasing deployment for this application [3]. The GaN LED offers higher energy efficiency and longer lifetime than an incandescent bulb. The importance is highlighted by the 2014 nobel price in physics which was awarded for developing the blue GaN LED [4]. In addition, GaN based blue laser diodes (LD) are commonly used in Blu-Ray optical disk data storage devices.

The wide band gap of GaN also results in a high breakdown field [5]. This combined with good thermal stability, heat conductivity and high electron mobility make GaN an excellent candidate for high performance electrical applications. Indeed, GaN based devices are seeing increasing deployment for radio base-station and radar applications [6]. In these applications, high power densities and high frequencies are required. GaN based high electron mobility transistor (HEMT) is suited for these challenges. A GaN HEMT exhibits high cut-off frequency and low onresistance [6]. Previously gallium arsenide (GaAs) based HEMTs were used. While GaAs has higher electron mobility, GaN has considerably higher breakdown field than GaAs. This means that a GaN amplifier can reach the same performance with less transistor stages.

In addition to radio applications, GaN is predicted to take over some part of power electronics such as frequency converters [7]. In these applications, the high sustainable power density and low on-resistance allows increased performance and efficiency [7]. Currently, most power electronic devices are based on either Si or silicon carbide (SiC). GaN offers higher performance compared to Si and lower device cost than SiC. However, SiC has higher breakdown field. Therefore, it seems that GaN is most suited for the voltage range between those of Si and SiC [5].

There has been an interest of manufacturing III-nitride (III-N) compounds since the semiconducting properties of III-V compounds were predicted in 1952 [8]. However, growth of GaN has proven difficult. Indeed, the first GaN LED was not demonstrated until 1971 [9]. In stark contrast, a red GaAsP LD was realized in 1962 [10]. The growth of high quality GaN is limited by the lack of suitable substrates. Foreign substrates typically have either a vastly different lattice constant or a different atomic arrangement compared to GaN. Moreover, common melt based growth processes cannot be used to grow bulk GaN substrates. Instead, GaN devices are almost exclusively grown on Si, sapphire or SiC [1,3]. The difficulty of growing

bulk GaN is due to the fact that GaN sublimates at atmospheric pressure instead of melting. It should be noted that native GaN substrates have been grown at extreme temperature and pressure conditions [11]. However, typically the size and quality of these substrates is not sufficient for commercial devices [11].

Metal-organic vapour phase epitaxy (MOVPE) is the most used method for III-N device growth [5]. MOVPE offers reasonably high growth rates with good material quality and multiple material compositions. Other methods such as molecular beam epitaxy (MBE) or hydride vapour phase epitaxy (HVPE) also exist. MBE offers lower impurity incorporation although at lower growth rates than MOVPE. On the other hand, HVPE has a higher growth rate than MOVPE but the achievable material compositions and crystal quality limit the usefulness of HVPE. At present, most commercial devices are processed with MOVPE, MBE is employed for materials research and HVPE is used to manufacture bulk GaN substrates [5].

Widespread use of GaN requires low device cost [1]. One way to decrease the cost is to use cheaper substrates. In addition, the use of larger substrates decreases the processing cost. The processing time and resources are almost independent of the wafer size but there are more chips per wafer on a larger wafer. Silicon substrates suitable for GaN growth are available at 8-inch size. Silicon substrates are considerably cheap, the price is about 1/10 of that of a sapphire substrate and about 1/100 of that of a SiC substrate [12]. In addition, it is suggested that some obsolete silicon device processing facilities could be re-purposed for GaN on Si device processing. However, growth of GaN on Si is challenging and the crystal quality is lower than for growth on sapphire or SiC. Therefore, it seems that GaN on Si is suitable for lower cost applications which still can benefit from the properties of GaN. These include lower voltage power electronics and general lighting where the acquisition cost is important [13].

Growth of GaN on Si is challenging because of the vastly different material properties. Indeed, the first GaN on Si LED was demonstrated as late as 1998 [14]. There is a considerable lattice mismatch (18%) and large thermal expansion coefficient mismatch (46%) between GaN and Si [2]. Moreover, GaN cannot be directly grown on silicon because gallium reacts aggressively with silicon at elevated temperatures [5]. Despite these challenges, device quality GaN can be realized on Si using appropriate intermediate layers. The lattice and thermal expansion mismatch can lead to high stresses and bowed wafers. Therefore, wafer bow and stress tailoring are required during growth [13]. In addition, the high initial dislocation density caused by the lattice mismatch needs to be reduced during growth.

The aim of this thesis is to study the MOVPE growth of GaN films on silicon. Firstly, the properties and MOVPE growth of GaN are introduced. A modern MOVPE apparatus for GaN on Si growth by Aixtron is presented. The apparatus is intended for growth on 6-inch silicon substrates. Then, the peculiarities of GaN on Si are discussed. GaN on Si growth process employing an AlGaN buffer layer scheme is discussed. Finally, the characterization of the grown structure is presented. White light reflection is used to assess layer thickness and the wafer profile is measured for the amount of bow after growth. The material quality is analysed with x-ray diffraction measurements.

# 2 Crystalline semiconductors

The aim of this chapter is to present the properties of crystalline solids and physics of semiconductors in order to understand the properties of gallium nitride. First, the concept of crystal lattice, lattice directions and planes are described. Then, general properties of semiconductors are presented followed by compound semiconductors. Finally, gallium nitride is considered from these perspectives.

# 2.1 Crystal lattice

Crystalline solids are materials that have ordered periodical structure in three dimensions unlike amorphous materials which lack long period ordering. Some materials can exist in different crystal or amorphous arrangements. However, certain materials are thermodynamically stable only in a form of a crystal. For example, GaN melt cannot be created at atmospheric pressure.

Single crystalline materials maintain the ordering in a certain piece of that material. On the other hand, polycrystalline materials have several regions that are periodically arranged. These regions, grains, are then misaligned with respect to one another. Therefore, the periodicity is not satisfied at the grain boundaries.

The atoms within a crystal are ordered so that the various inter-atomic distances and orientations are constant throughout the material. The particular set of periodic arrangements of atoms is called a lattice. There are 14 possible different lattices [15].

Lattices are defined by unit cells. The unit cell is the smallest periodic arrangement of atoms in a certain lattice. The entire lattice can be then constructed by placing unit cells next to each other. The unit cell is span by lattice vectors. Three vectors are required to span a three dimensional space. Lattice vector translation from a lattice site leads to a similar lattice site. In other words, the lattice can be constructed using lattice vectors in addition to using unit cells. The magnitudes of lattice vectors are called lattice constants.

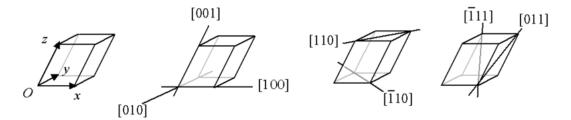

Direction of a line in a lattice is typically described using the unit vectors. Figure 1 presents some directions in a lattice. A line passing through the origin and a point (u,v,w) can be described as having the direction of (uvw). Any direction can be then described this way by first drawing a parallel line through the origin. Note that the indices u v w are not necessarily integers. However, the indices can be converted to the smallest possible set of integers. Therefore  $\left[\frac{1}{2}\frac{1}{2}1\right]$ ,  $\left[112\right]$  and  $\left[224\right]$  represent the same direction. However,  $\left[112\right]$  is the preferred form. Negative indices are written with a bar over the number, for example  $\left[\bar{1}12\right]$ .

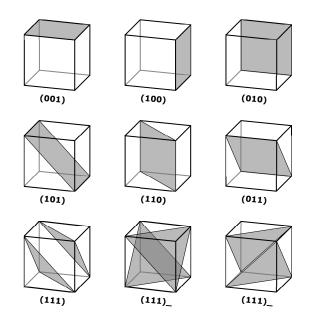

Miller indices are used to distinguish crystallographic planes. Figure 2 presents some Miller indices of planes in a cubic crystal. Consider a plane in a lattice which dissects a unit cell with lattice vectors  $\mathbf{a}$ ,  $\mathbf{b}$  and  $\mathbf{c}$ . Now, the plane intersects the axes of the unit cell. The distance of the intersection points  $\mathbf{x}$ ,  $\mathbf{y}$  and  $\mathbf{z}$  are measured along the lattice vectors from the origin. Next, the respective lattice vector length is divided with the interception point distance from the origin. Thus,  $(\mathbf{h}\mathbf{k}\mathbf{l}) = (\frac{|\mathbf{a}|}{x}, \frac{|\mathbf{b}|}{y}, \frac{|\mathbf{c}|}{z})$ . This is convenient as the lattice vectors can have different lengths. In addition, a plane that is perpendicular to a certain crystallographic axis has the Miller index

Figure 1: Various lattice directions [16].

of zero. In short, the Miller indices are defined as the reciprocals of the fractional intercepts that the plane has with the lattice vectors. Similar to lattice directions, a negative Miller index is denoted with a bar over the number.

Figure 2: Miller indices in a cubic system [17].

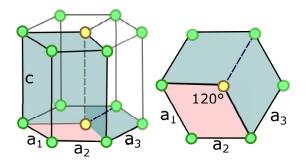

Figure 3: Hexagonal lattice with one unit cell highlighted. Adapted from reference 18.

Hexagonal crystal system can be indexed similarly, although a four index notation (hkil) is also commonly used. As any crystal, the hexagonal system can be

defined using three lattice vectors hkl. The fourth index i highlights the crystal symmetry. Figure 3 presents the hexagonal lattice. One rhombic unit cell of the hexagon is highlighted. Three unit cells are required to complete the hexagonal atomic arrangement.

In the case of the four index notation, three vectors  $\mathbf{a_1}$ ,  $\mathbf{a_2}$  and  $\mathbf{a_3}$  define a basal plane. The angle between these vectors is 120° and  $|\mathbf{a_i}| = a$ . This angle results in a six-fold symmetry of the crystal. It also follows that  $-\mathbf{i} = \mathbf{h} + \mathbf{k}$ . The fourth lattice vector  $\mathbf{c}$  is perpendicular to the basal plane and it defines the separation of two basal planes.

#### 2.2 Semiconductors

Semiconductors are materials whose conduction properties can be altered. In a crystalline semiconductor electrons cannot have arbitrary combinations of momentum and energy. Instead, the electrons typically reside in two energy regions that are separated. The electrons can transfer between these regions if the electron energy is altered sufficiently.

The energy regions are typically explained using the energy band model. The energy band model can be derived from quantum mechanical considerations. The electronic binding force between the atom core and the electrons can be simplified to a potential well. Now, when a vast amount to atoms are brought to close proximity, the potential wells start to overlap. The electrons closest to the core are still tightly bound. However, the electrons that are close to the well edges are no longer effected by only one core. A periodic potential is formed whose properties are defined by the inter-atomic distance and electric attraction. This periodic potential allows some electrons within a specific energy range to tunnel through the potential barriers. Thus, some electrons can move in the material. However, the electrons cannot have the same wavenumbers as stated by the Pauli exclusion principle. Therefore, a continuous spectrum of electron energies is formed around the suitable energy value for tunneling, and it is called an energy band.

The concept of Fermi level is closely related to electronic band structure. The Fermi level is defined as the highest energy that the electrons occupy at 0K or the energy where the occupation probability is 50%. In the case of intrinsic or moderately impure semiconductors, the Fermi level is located between two energy bands. The band above the Fermi level is called the conduction band. Conversely, the band below the Fermi level is called the valence band. The energy region between the bands without electrons is called the band gap. It should be noted that for high impurity concentrations, the Fermi level can coincide with a band.

The energy band model can be used to explain electrical and optical properties of a material. An empty or a full band cannot conduct electricity. Either electrons or local deficit of electrons can contribute to an electrical current. The lack of one electron is typically modelled as a quasi particle with a positive charge called a hole. Together electrons and holes are referred to as charge carriers.

In metals, the Fermi level resides within a band. Therefore, the highest band is partially filled, which explains the good conductivity. On the other hand, insulators

have a large energy separation, band gap, between the bands. In addition, only the valence band is filled with electrons. Thus, the electrical conductivity of insulators is low. Semiconductors are somewhere between these two extremes. The band gap of semiconductors is smaller than the band gap of insulators. At low temperatures, semiconductors work as insulators. However, at room temperature, thermal energy is usually sufficient to excite electrons to the conduction band from the valence band. As a result, semiconductors show some conducting properties.

The division of materials to semiconductors and insulators is somewhat arbitrary. Semiconductors are characterized by their usefulness in electrical components. For these applications it is required that the density of electrons between the bands can be altered.

The electrical properties of semiconductors can be altered by introducing minute amount other suitable materials into the semiconductor lattice. This process is called doping. If atoms with more valence electrons than the host material are introduced, the Fermi level is effectively raised. Thus, the valence band becomes filled and the excess electrons are raised to the conduction band. This type of semiconductor is called n-type where the majority charge carrier is an electron. The conduction in an n-type material arises from the partially filled conduction band with excess electrons. On the other hand, if atoms with less valence electrons are introduced, p-type material is created. A p-type material has a lower Fermi level and the majority charge carrier is a hole. In the case of a p-type material, the conduction is caused by the holes in the partially filled valence band.

Optical properties of semiconductors can be explained using the magnitude and alignment of the band gap. Electrons can be excited from the valence band to the conduction band if sufficient energy is provided. Therefore, only photons with equal or greater energy than material band gap have significant absorption. Similarly, a semiconductor most likely emits photons with with an energy close to the band gap energy.

The band alignment significantly affects the photon absorption probability. In a direct band gap material, electrons can be excited directly from the valence band to the unoccupied states of the conduction band. However, in a indirect band gap material, the valence band maximum and the conduction band minimum are not located at the same electron momentum. Therefore, the electron momentum must also be changed in the absorption process. Photon momentum is small compared to the electron momentum. The impulse is provided by a phonon, the quantum of lattice vibration. This simultaneous interaction of an electron with a photon and a phonon is considerably less probable than excitation in the case of the direct band gap. Thus, the absorption and emission in indirect band gap semiconductors is weak compared to those in direct band gap materials. In optoelectronic applications, direct band gap materials are preferred. However, it can be beneficial to employ indirect band gap materials in segments where either absorption or emission is unwanted.

# 2.3 Compound semiconductors

Compound semiconductors are material systems that consist of two or more types of atoms. The most commonly used material systems in optoelectronic applications are the III-V semiconductors. The III-V semiconductors consist of group III and group V elements. These elements do not exhibit semiconducting properties by themselves. In addition, typically the physical properties of these elements differ significantly. For example, aluminium is a commonly used metal and nitrogen is a gas. Still, these two elements can form aluminium nitride under suitable conditions. Only when brought together into a thermodynamically stable lattice the semiconducting properties appear.

The history of compound semiconductors starts in the early 20th century. Although the III-nitride based devices have a shorter history than the III-arsenide or III-phosphide applications, the nitride compounds were discovered first. AlN, InN and GaN were first reported in 1907, 1910 and 1932 [19], respectively. The semiconducting properties of III-V compounds was predicted in 1952 [8]. Only ten years later in 1962, a red GaAsP laser diode was realized [10]. A plethora of optoelectronic devices, crystal growth and characterization methods soon followed.

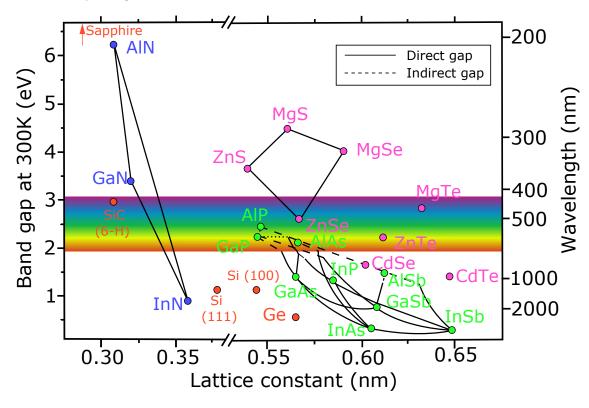

Figure 4: Energy band gaps and lattice constants of semiconductors. The alloy group that the semiconductor belongs to is represented with a colour: III-nitrides (blue), other III-Vs (green), II-IVs (pink) and intrinsic semiconductors (red). The coloured area illustrates the colour of light emitted by the semiconductor. Adapted from reference 20.

Figure 4 presents the various band gaps and lattice constants of most commonly

used III-V semiconductors and other semiconducting material systems. The III-V semiconductors can be alloyed in order to engineer the lattice constant and the band gap almost at will. However, it should be noted that certain alloys are difficult to realize in high quality due to the miscibility gap. Nevertheless, these semiconductor alloys span a wide region in terms of lattice constants and band gaps. Importantly the optical region can be covered from deep UV to near infra red. In addition, other electrical, mechanical and chemical properties of the alloys can differ significantly. Furthermore, the conductive properties can be altered by doping. Thus, p- and n-type materials can be created and typical (opto)electical components realized.

Compared to silicon and other elemental semiconductors, compound semiconductors allow more device applications. Most important is the ability to employ quantum confinement in heterostructures. In a heterostructure, a material region is surrounded by higher band gap material. Therefore, charge carriers can be confined in the low energy region. This local increase of charge carrier density can increase the efficiency of devices. In addition, heterostructures can be employed in field effect transistors (FET). The confinement in addition to doping is used to create two-dimensional electron gas. These transistors exhibit very high electron mobilities as the channel is located in a dopant free region.

Some compound semiconductors show piezoelectric properties. Piezoelectricity can be exploited in the FETs to enhance the creation of the electron gas. It could be possible to create piezoelectric bulk acoustic filters for radio frequency applications. On the other hand, piezoelectricity hinders the performance of optical devices. The piezoelectric potential lowers the spatial overlap of charge carriers in the quantum confined regions, an effect called quantum confined stark effect. The band gap type can be either direct or indirect depending on the semiconductor alloy. In the active area of an optical device, direct band gap is typically chosen.

On the left side of figure 4 are the III-nitride alloys: one subset of the III-V semiconductors (AlN, GaN and InN). These alloys are characterised by a wide band gap together with a good thermal and chemical stability. Therefore, III-Ns are suitable for short wavelength optical applications and high performance electrical components. However, the lattice constant of these alloys differs significantly from other common semiconductor compounds (figure 4). Moreover, the III-Ns preferably crystallize into a wurtzite lattice as opposed to the cubic lattice of most III-V semiconductors. This poses a challenge in manufacturing the III-N alloys as there is a limited amount of suitable substrates.

#### 2.4 Gallium nitride

Gallium nitride (GaN) is a compound semiconductor that belongs to the III-nitride group of III-V semiconductors. GaN has a direct band gap of 3.42 eV at 300 K [2]. This makes GaN suitable for optoelectronic applications, most notably blue LEDs. In addition, the wide band gap results in a high breakdown field. Combined with sublimation point exceeding 1400 °C [2, 21], good thermal conductivity and high electron mobility [2], GaN is an excellent candidate for high performance electrical applications. Indeed, there is increasing deployment of GaN based components in

wireless infrastructure, radar applications and power electronics [6,7].

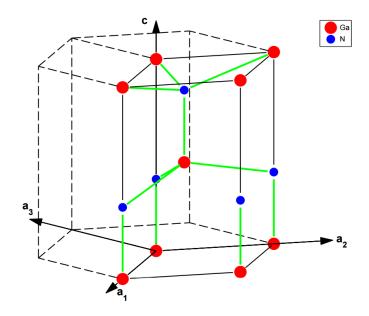

Figure 5 presents the crystal structure of wurtzite GaN with one unit cell high-lighted. GaN crystallizes either in wurtzite or zinc blende structure, former being more stable and common. Properties of other III-N semiconductors are listed in table 1.

Figure 5: Wurtzite structure of GaN [22].

Table 1: Properties of III-N semiconductors [2].

|                                                            | GaN    | AlN    | InN    |

|------------------------------------------------------------|--------|--------|--------|

| Band gap 300 K (eV)                                        | 3.42   | 6.2    | 0.78   |

| Lattice constant a (nm)                                    | 0.3189 | 0.3112 | 0.3538 |

| Thermal expansion coefficient $\Delta a/a \ 10^-6 \ (1/K)$ | 5.6    | 4.2    | 3.2    |

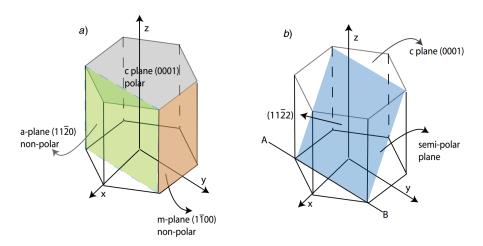

Wurtzite GaN is a polar material with respect to the [0001] c-axis. Depending on the type of atoms that occupy the lattice sites at the c-planes, GaN is either Gapolar or N-polar. Figure 5 shows the Ga-polar configuration. In addition, the GaN structure deviates slightly from the theoretical structure. The nearest neighbour distance is about 0.5% larger than the ideal value [2]. In the case of GaN, the nearest neighbour distance is the distance between Ga and N atoms in the c-axis. Therefore, there is an intrinsic electrical field in a GaN crystal. In addition, strain in the crystal causes piezoelectric polarization. However, planes perpendicular to the c-plane, a-plane and m-plane, do not exhibit polarization (figure 6a). Planes angled with respect to the c-plane show some polarization (figure 6b). The polarization

effects can be either detrimental or beneficial for electrical devices depending on the application. Thus, there is a focused research for growing GaN in different orientations [5,23].

Figure 6: Schematic diagram of a) polar and non-polar crystal planes and b) an example of a semi-polar GaN wurtzite crystal plane [24].

# 3 MOVPE

In this chapter, metal-organic vapour phase epitaxy (MOVPE) growth is discussed. The principle, growth modes and the growth regime of a MOVPE process are discussed. Finally, MOVPE growth of GaN is considered.

MOVPE is the most commonly used growth method for fabricating compound semiconductor materials on an industrial scale. Other deposition methods exist, such as hydride vapour phase epitaxy (HVPE) or molecular beam epitaxy (MBE), but MOVPE has several advantages over the other technologies. A MOVPE reactor can reach higher growth rates than MBE and, on the other hand, produce higher quality layers than HVPE although at lower growth rates. Furthermore, MOVPE can produce a wide range of material combinations. At present, HVPE is mainly employed for producing substrates, MBE is mainly used for material research purposes and most of commercial devices are processed with MOVPE.

The growth process in MOVPE is based on chemical reactions of organometallic compounds as opposed to MBE where physical deposition (phase transition) is employed. In the case of HVPE, chemical reactions of metal chlorides are used.

# 3.1 Operation

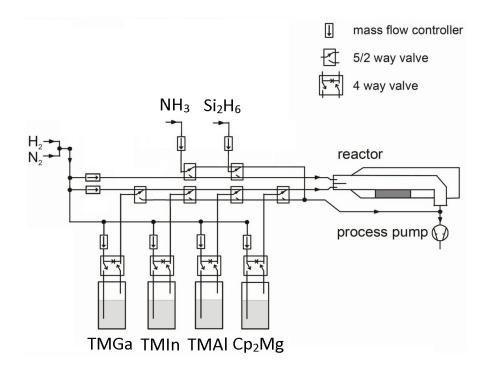

Figure 7: Schematic diagram of the gas lines of a MOVPE apparatus. Adapted from 25.

Figure 7 schematically presents the gas lines in a MOVPE apparatus. Sophisticated gas control is required in order to ensure stable growth rates and, on the other hand, realize step-like material interfaces. Precursor materials are brought

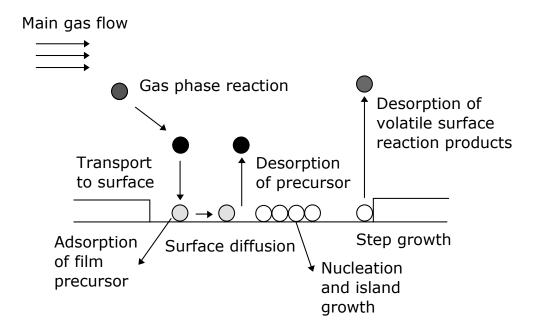

Figure 8: Transport and reaction processes in MOVPE. Adapted from reference 26.

to the reactor in a diluted mixture with a carrier gas, that is usually hydrogen or nitrogen. The carrier gas is used to transport and dilute the liquid phase precursors. The liquid phase source materials are in containers called bubblers. The carrier gas flows through a bubbler and a source material liquid. Some of the source material is absorbed by the carrier gas and, as a result, a saturated vapour is formed. The bubbler temperatures are controlled to obtain suitable vapour pressures. In addition to the host semiconductor materials, dopants are required to fabricate p- and n-type materials.

The reaction chamber is usually made from quartz or stainless steel in order to limit the reactions between reactor walls and gases. In addition, some reactor types have separate inlets for group III and group V precursors to limit parasitic reactions between the precursors, that is, reactions without material deposition.

Growth in a MOVPE reactor is based on chemical reactions of metal-organics, organic compounds and hydrides (figure 8). Inside the reactor there is a heated susceptor that holds the substrate. The growth temperature is in the metastable region of the desired semiconductor material. The precursors decompose on the substrate in a reaction called pyrolysis. The atom in the precursor that will form the desired semiconductor separates from the other precursor molecule atoms. The separated atom diffuses to the substrate where it can be incorporated to the new crystalline layer. The by-products out-diffuse and are removed by the carrier flow. The carrier gas does not participate in the chemical reaction although there can be inadvertent incorporation into the growing layer. Moreover, there is some by-product incorporation, mostly carbon.

Under optimal conditions the formed layer is epitaxial; the grown layer copies the structure of the underlying substrate. The growth conditions promote lateral diffusion on the substrate and nucleation into lattice sites. On the other hand, atoms that do not bond into lattice sites are desorbed. In addition to deposition, etching of the semiconductor layer can occur depending on the reactant concentrations, temperature, pressure and the type of carrier the gas.

#### 3.2 Growth mode

Three different growth modes can be identified in epitaxy. These are Frank-van der Merwe (FM), Stranski-Krastanov (SK) and Volmer-Weber (VW) growth modes. The dominating growth mode depends on the various ad-atom interactions compared to the ad-atom surface interaction strength. These interactions are affected by the difference in lattice constant of the substrate and the overlayer in equilibrium, electronic hybridization at the interface and accumulated volume strain [27].

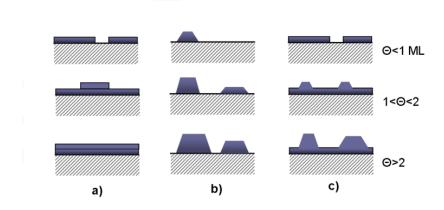

Figure 9: Cross-sectional view of growth modes in thin film growth: a) Frank-van der Merwe, b) Volmer-Weber and c) Stranski-Krastanov.  $\Theta$  denotes the epitaxial layer thickness in monolayers. [28].

Figure 9 presents the three growth modes. The FM mode is essentially a 2D growth mode, in which each atomic layer is completed before next one begins to form (figure 9a). In the case of the FM growth mode the interaction between the ad-atoms and the substrate dominates. In contrast, the VW growth mode forms islands or aggregates of atoms (figure 9b), because the ad-atom interactions are stronger than the interactions with the substrate. Typically, defects are created to the substrate-island interface to relief strain and these defects propagate to the islands. The VW growth mode can be classified as 3D growth. However, if growth is continued sufficiently long the islands can merge. Unfortunately, structural defects can be created at the interfaces between the islands. On the other hand, the SK growth mode undergoes a transition as the relative contribution between ad-atom and surface adhesive force changes as a function of film thickness (figure 9c). The growth starts with a thin strained 2D layer called the wetting layer. After the critical thickness, 3D islands begin to form on the wetting layer. Opposed to the VW growth mode, the SK mode can relieve the stresses coherently without generating defects

in the substrate-island interface. As with VW growth, the islands can coalescence to a film if growth is sustained.

# 3.3 Growth regime

Three growth regimes can be identified in typical MOVPE growth process as a function of temperature. These regimes are classified by the dependence of growth rate as a function of temperature and the physical processes causing the differences. At low temperatures (450-550 °C), the growth rate increases with increasing temperature according to the Arrhenius equation

$$V_{growth} \propto \exp \frac{-\Delta E}{RT},$$

(1)

where  $\Delta E$ , R and T are the energy potential associated to the limiting kinetic process, the ideal gas constant and temperature, respectively. This is know as the kinematic regime. The growth rate can be limited by, for example, the desorption kinetics of  $CH_3$  molecules. Based on equation 1 it can be seen that the growth rate is heavily dependent on temperature. Kinetic regime is typically used for the nucleation layer deposition in the growth of GaN. The low temperature allows adatoms to bind and remain in surface sites with low binding energy. Therefore, the parameter space for material deposition is relaxed. However, the material quality is low.

When the system has sufficient thermal energy, the growth rate is no longer limited by reaction kinetics. Instead, gas phase transport of precursor materials on the surface becomes the limiting factor. This is known as the mass transport limited growth regime, in which the growth rate has a weak temperature dependence

$$V_{growth} \propto \rho D \nabla Y_{MO},$$

(2)

where  $\rho$ , D,  $\nabla Y_{MO}$  are the gas density, diffusion coefficient and the gradient of the metal-organic species mass fraction between the surface and the reactor atmosphere, respectively. The growth is mass transport limited in moderate temperatures, approximately from 550 °C to 850 °C. The temperature dependence can be approximated with the following considerations. Gas density is inversely proportional to temperature

$$\rho \propto T^{-1},\tag{3}$$

whereas diffusion constant is exponentially proportional to temperature

$$D \propto T^{1.7}. (4)$$

Therefore, the growth rate in mass transport limited growth is weakly dependent on temperature

$$V_{growth} \propto T^{0.7}$$

. (5)

The mass transport limited growth rate is not inherently dependent on pressure as gas density is directly proportional to pressure

$$\rho \propto p,$$

(6)

and on the other hand, diffusion constant is inversely proportional to pressure

$$D \propto p^{-1}. (7)$$

Thus, these two contributions negate each other. However, pressure has an effect on the reaction kinetics and, therefore, can have an effect on the growth rate.

The third growth regime is reached at high temperatures. Typical growth temperatures are over 850 °C. Here, growth can still be classified as being mass transport limited. However, the desorption/etching rate of the surface is significant compared to the growth rate and, therefore, the growth rate decreases with increasing temperature. High growth temperature increases the crystal quality. Ad-atoms that are not bound to high binding energy lattice sites are desorbed. Especially for GaN growth higher pressures and increased  $H_2$  content compared to  $N_2$  or metal-organic species increase the etch rate.

#### 3.4 Growth of GaN

An optoelectronic device can operate efficiently in a wavelength region close to the material band gap. As a result, the III-arsenide and the III-phosphide devices are suitable for wavelengths from the near infra red to yellow light (figure 4). On the other hand, the III-nitride compounds span almost the entire light spectrum (figure 4). Therefore, there has been a large interest to realize III-nitride based optoelectronic devices. Especially efficient blue and green LEDs were sought after. However, growth of epitaxial III-Ns proved to be difficult and the first blue LED based on GaN was demonstrated as late as 1971 [9]. The most serious issues in growth were the crystal quality and the effective doping of GaN.

The chemical reaction producing GaN in a MOVPE reactor can be simply described as

$$Ga(CH_3)_3 + NH_3 \rightarrow GaN + 3CH_4.$$

(8)

In this case, one trimethylgallium (TMGa) molecule reacts with one ammonia  $(NH_3)$  molecule to produce gallium nitride and three methane molecules. However, the intermediate chemical species and competing reaction pathways are considerably more complex [29]. TMGa and  $NH_3$  are the most common precursors for GaN growth in MOVPE. In addition, triethylgallium (TEGa) and hydrazine  $(N_2H_4)$  are sometimes employed as Ga and N precursors, respectively. Hydrogen is typically used as a carrier gas. It should be noted that using nitrogen carrier gas as a precursor is not viable as nitrogen gas is too stable to create atomic species [29]. Nitrogen or mixture of nitrogen and hydrogen carrier gas is employed when growing InGaN-alloys.

GaN growth requires high temperatures, typically over 1000 °C, for high quality. This is due to the fact that the temperature has to be in the metastable region where the material desorption is significant. Thus, incorporation into lattice sites is preferred. Significant sublimation of GaN occurs at over 1000 °C [2,21]. This temperature can be regarded as the first approximation for the growth temperature. Furthermore, the effective pyrolysis of  $NH_3$  requires high temperatures [29]. At these temperatures, the disassociation pressure of nitrogen from GaN is high. Therefore, high III/V-ratios are used to provide nitrogen rich atmosphere. High nitrogen concentration limits the decomposition of the crystal.

Typical dopants are disilane  $(Si_2H_6)$  and bis-cyclopentadienyl magnesium  $(Cp_2Mg)$  for n-type and p-type GaN, respectively. One of the challenges of device fabrication is the low quality of p-type GaN. As-grown Mg-doped GaN shows high resistivity. Thermal activation of Mg dopants is required to realize p-type material. The Mg acceptors are passivated by hydrogen during growth. Even after annealing, the resistivity of p-GaN is high and on the other hand the hole concentration is low. Conversely, the conductivity of n-type GaN is about two magnitudes higher. The poor characteristics of p-type GaN are due to the high activation energy of Mg acceptors in the crystal. The activation energy value is about 160-200 meV [2, 30]. Thus, at room temperature only 6% of the acceptors are activated [30]. Other group II elements have been studied for p-type doping. However, it seems that although Mg doping is not optimal, the alternative dopants studied do not improve the electrical properties due to poor solubility or activation energy [2, 30].

# 3.5 Substrates for GaN epitaxy

The lack of high quality native substrates is a serious obstacle in epitaxial growth of III-nitrides. Whereas substrates for phosphide and arsenide compounds (eg. GaAs, InP) can be grown using standard Czochralski or Bridgman-Stockbarger processes, melt based growth of III-nitrides is not viable. There are two main causes for this. Firstly, the melting points of III-nitrides are high. For instance, the theoretical melting point of GaN is 2500 °C [2]. Furthermore, the disassociation pressure of nitrogen at that temperature is estimated to be 45 000 atm [2]. Therefore, it is clear that GaN melt cannot be created at least without extreme conditions.

GaN is widely grown on non-native substrates, although native ammonothermally grown substrates exist [11]. However, native substrates are not available at high quality and sufficient sizes. Sapphire, Si and SiC are the most used substrates for epitaxial growth of GaN. The use of these substrates presents challenges especially in lattice mismatch, thermal expansion mismatch and, in the case of silicon, chemical stability. It is evident that the substrate choice is a compromise between factors such as price and lattice mismatch together with electrical, chemical and mechanical properties.

Early experiments of GaN growth were performed on sapphire substrates. C-plane (0001) sapphire  $(Al_2O_3)$  is somewhat compatible with c-plane GaN despite the considerable 13.9% lattice mismatch and moderate thermal expansion coefficient (34%) mismatch. However, by employing an AlN interlayer and using coincidence

site epitaxy, high quality GaN layers can be realized. Sapphire presents a challenge for device processing as an insulating substrate. Either contacts have to be deposited on the front side of the wafer or the wafer has to be removed. Moreover, the thermal conductivity of sapphire is low compared to Si or SiC. From this point of view, sapphire is not a good candidate for high performance applications. However, the high electrical resistivity can improve the breakdown field of the device in power applications. The price of sapphire substrates is moderate, between silicon and SiC.

SiC substrate offers some of the best properties for GaN growth. From a growth perspective, SiC offers low lattice (3.5%) and moderate thermal expansion coefficient (25%) mismatch. On the other hand, SiC has high breakdown field and high thermal stability. SiC has a sublimation temperature of 2730 °C [5]. In addition, SiC has higher thermal conductivity than sapphire or Si. These properties make SiC an excellent substrate for high performance applications. However, manufacturing of high quality SiC substrates is difficult and expensive. As with GaN bulk substrates, melt based processes can not be used. Moreover, over 4-inch wafer sizes are not yet available at suitable quality. This increases the chip cost as processing price for a wafer is more or less the same but there are less chips per wafer. Thus, SiC substrates are commonly limited to high end components. However, III-N component manufacturers have found niches for their products. For example, a range of LEDs on cheap silicon substrates to high performance SiC variants are available.

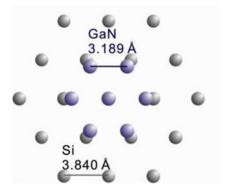

Figure 10: Superimposed atomic arrangements of a (111) oriented silicon substrate and a c-plane of wurtzite GaN lattice. Adapted from reference 23.

Silicon is the newest widely adopted substrate choice for GaN growth. Although silicon substrates are extensively used in microelectronic industry, the adoption for GaN growth has been challenging. Major challenges arise from the mechanical and chemical differences between Si and GaN. Nevertheless, silicon substrates for III-N devices have received increasing interest. High quality Si substrates are available up to 12-inch size. GaN is commonly grown on (111) oriented silicon substrates. Although at this time only 8-inch (111) oriented silicon substrates are widely available. Figure 10 presents the atomic arrangements of silicon cut along (111) plane and c-plane of wurtzite GaN. It can be seen that the atomic configurations are compatible. However, there is a considerable lattice mismatch (17%) and large thermal expansion mismatch (46%) between Si and GaN [13]. MEMS processing on (111) oriented

silicon substrates is fairly typical meaning that substrates are available at low cost, although microelectronics industry prefers (100) orientation. Furthermore, processing tools for silicon substrates are readily available. In addition, it is suggested that some obsolete silicon device processing facilities could be re-purposed for GaN on Si power electronics processing. Integrating GaN based electronics with Si-CMOS is a promising long term goal. It might be possible to exploit the piezoelectricity of GaN to create acoustic wave filters for radio applications [31].

# 4 Aixtron 1x6" CCS MOVPE

The Aixtron 1x6" close coupled showerhead (CCS) MOVPE apparatus is configured for III-nitride growth on 6-inch wafers. This reactor has some modern features targeted for III-nitride growth on silicon wafers such as a multi-zone heater and extensive in-situ monitoring. This chapter considers the system characteristics and in situ instruments.

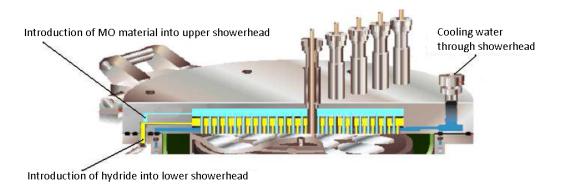

# 4.1 System

The apparatus has a radial flow reaction chamber where the precursors are introduced perpendicular to the substrate and are evacuated at the edges. Figure 11 presents the flow channels in the reactor lid. There are two plenums on top of the substrate from which III and V group precursors are provided. There are two separate flow channel arrays in close proximity to the wafer, an arrangement resembling a showerhead. Some flow channels on the showerhead can be used as optical windows for in situ monitoring. The system is a cool wall reactor; the showerhead is cooled by water flow. The design is intended to limit the parasitic reactions that can be significant in III-N material growth. Firstly, mixing of the precursors takes place in the reaction chamber. Furthermore, the pyrolysis reactions occur at the substrate surface. In addition, the CCS scheme improves uniformity.

Figure 11: Close coupled showerhead reactor lid of the Aixtron MOVPE apparatus [32].

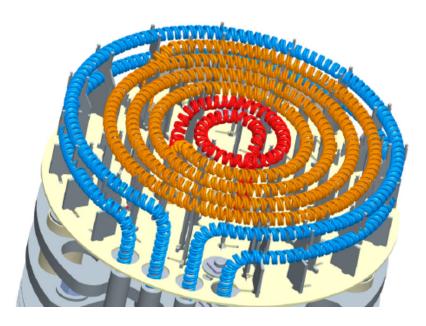

The substrate is placed on a SiC coated graphite susceptor. The SiC coating is used to improve thermal and chemical stability of the susceptor. The susceptor rotates in order to provide uniform temperature profile and precursor concentration. The susceptor is heated from underneath using three tungsten coils. The arrangement of these coils is presented in figure 12. The coils form three radial zones. These zones can be utilized to fine tune the radial temperature profile of the susceptor. This is beneficial as the substrate bows during growth. Therefore, the substrate surface temperature and bowing can be controlled.

The reactor provides two temperature values. The first value is the susceptor temperature. This value is measured with thermocouple that is located under the

susceptor in a close proximity to it. The second value is given by the in situ measurement setup which is discussed in the next chapter. The in situ measurement setup monitors either the susceptor surface temperature or the wafer surface temperature depending on whether there is a wafer in the reactor. It should be noted that the difference between the thermocouple temperature value and the measured wafer surface temperature can be over 200 °C during growth.

Figure 12: Three susceptor heater zones of the Aixtron MOVPE apparatus [33].

Thermal control is especially important as the substrate size is increased. Larger substrates are more prone to cracking because the thermal and mechanical stresses are more pronounced. In addition, III-nitride growth is characterized by lattice and thermal mismatches between the substrate and the epitaxial layers. Moreover, the incorporation of indium in the InGaN alloy is extremely dependent on temperature. Therefore, strain engineering and thermal control are vitally important.

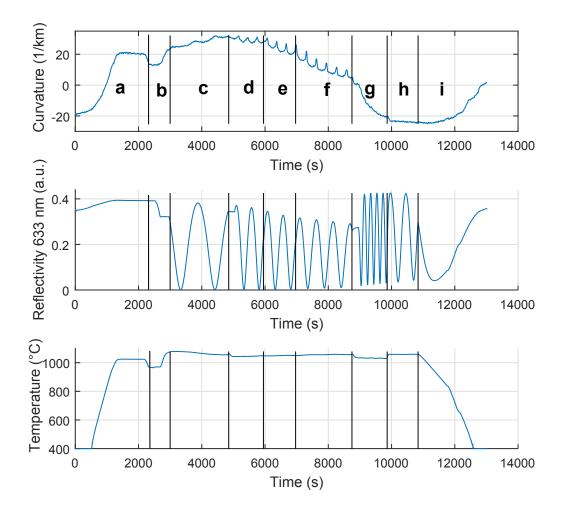

# 4.2 In situ monitoring

In situ monitoring of the growth process has become vital for high quality material growth by MOVPE. These type of instruments provide better insight about the conditions during growth, thus allowing better optimization of the growth process. In addition, as growth conditions vary, some critical processing steps might require active recipe control. For example, in the case of GaN on sapphire, nucleation has major impact on the epitaxial layer quality. Therefore, nucleation could timed using reflectance of the surface to ensure appropriate formations. In situ monitoring allows to fabricate more delicate structures and, on the other hand, reduce variance between growth runs.

In some cases, in situ monitoring can reduce the need for other characterization equipment. As there may not be a need to employ an external tool, process development can accelerate. In addition, it can be more accurate to characterize the individual layers as they form as opposed to extracting information from the complete film stack. However, characterization tools such as x-ray diffraction and Hall measurement are usually required. Nevertheless, the data provided by in situ monitoring could be correlated with that obtained by other characterization tools. In this case, some samples would be characterized with the external instruments.

Typical in situ measurements include layer thickness, wafer curvature and surface temperature measurements. The measurements are usually conducted optically. Physical contact with the substrate is usually not possible due to high temperatures, pressure gradients and delicate gas flows. Flow ports on metallic wall reactors can be employed as optical paths. On the other hand, instrument placement on quartz reactors can be easier.

Reflectance measurements can be utilized to assess surface morphology and film thickness. The thickness measurement is based on simple Fabry Perot oscillations. A laser beam is reflected from the sample surface and focused to a detector. Layer thickness (growth rate) can be resolved from the period of the oscillations. In addition, material quality and composition can be estimated based on the oscillation amplitude. More information on the film properties can be extracted by fitting a simulated curve to the measurement.

The reflected intensity is a sum of the reflection from the film surface and interferences inside the film stack. Considering a simple one layer model with a absorbing substrate, the reflectance has a maximum when the path difference equals an integer multiple of the wavelength

$$2nd = m\lambda, \quad m \in \mathbb{N},\tag{9}$$

where n is the refractive index of the film, d is the film thickness and  $\lambda$  is the wavelength. Similarly, the reflectance has a minimum when the path difference is equal to an integer multiple plus half wavelength

$$2nd = (m + \frac{1}{2})\lambda, \quad m \in \mathbb{N}. \tag{10}$$

The reflectance at the air film interface is given by

$$R = (n-1)^2 + \frac{k^2}{(n+1)^2} + k^2, \tag{11}$$

where n and k are the refractive index and extinction coefficient of the film, respectively.

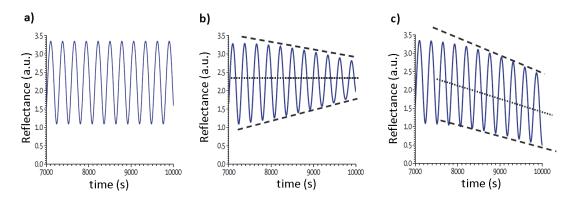

Figure 13 schematically presents three cases of in situ reflectance measurement. Ideal growth is characterized by constant amplitude and stable average reflectivity (figure 13a). Slight growth rate variations under the measurement area cause the reflectivity amplitude to decrease while the average reflectivity stays constant (figure 13b). On the other hand, increasing surface roughness decreases the average of the reflectivity (figure 13c). It should be noted that these two unideal cases are not mutually exclusive.

The MOVPE apparatus used in this work has Laytec Epicurve TT in situ measurement setup. Reflectance is measured at three different wavelengths, 405 nm, 633 nm and 950 nm. Three lasers are focused at normal incidence on the subsrate through optical ports on the showerhead. The reflectance can be measured at different spots along the same radius as the susceptor rotates.

Figure 13: Three cases of wafer surface evolution based on in situ reflectance measurement: a) ideal growth, b) growth rate variations and c) increasing surface roughness [34].

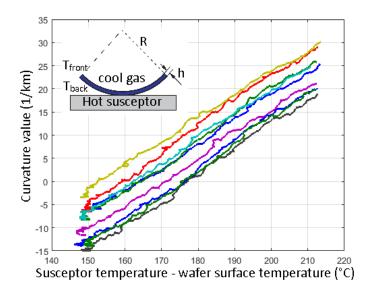

Wafer curvature measurement has become important as wafer sizes have increased. There are mainly two reasons. Firstly, the change in wafer curvature allows to have an estimate of the stresses on the substrate and epitaxial layers. On the other hand, tolerances for wafer bow in processing have become more strict as wafer size is scaled up.

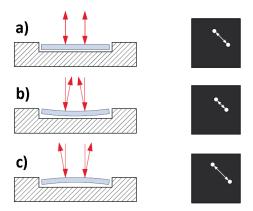

Figure 14 schematically presents optical wafer curvature measurement. The Epicurve TT measures the wafer curvature by focusing two parallel 405 nm wavelength laser beams on the substrate at normal incidence. The reflected beams are directed to a CCD array. The deviation of the laser spots on the CCD array is then converted to an estimate on the wafer curvature. In the case of a flat wafer, the spot separation stays constant (figure 14a). On the other hand, concave (convex) curvature causes the separation to decrease (increase), figure 14b (c).

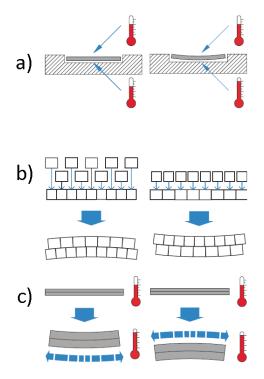

Figure 15 presents three factors for wafer curvature change. Temperature gradients will bend the wafer as thermal expansion affects the wafer non-uniformly. In figure 15a, the wafer back temperature is higher than the wafer surface temperature. Thermal expansion causes concave wafer bow. This is typical for heated susceptor reactors. In figure 15b, lattice mismatch induces stresses between the layers. On the left (right) side, epitaxial layer that has greater (smaller) lattice constant than the substrate is grown. The stress induced causes convex (concave) wafer bow. Finally, layers with different thermal expansion coefficients experience thermal stress when the temperature is varied (figure 15c). On the right (left) side the lower (upper) film has higher thermal expansion coefficient. The film stack temperature is increased and concave (convex) wafer bow is observed. It should be noted that the wafer curvature and temperature profile are connected as the wafer contact to the susceptor changes with varying wafer curvatures.

Figure 14: Optical in situ wafer curvature measurement. The wafer on the susceptor and the paths of the laser beams are shown at left and the laser spots on the CCD array at right for a) flat, b) concave and c) convex wafer. [34].

Figure 15: Effect of a) thermal gradient, b) lattice mismatch and c) different thermal expansion coefficients of layers on the wafer curvature [34].

The surface temperature of the wafer is obtained by fitting a black body radiation curve to the infra-red emission of the wafer. The measurement can be conducted either using two or more detectors with different band pass filters or with one CCD detector. In the case of the CCD detector, the emission spectrum is split with a

prism. In both cases, relative intensities of certain wavelength regions are used. For accurate measurements the wafer emissivity is estimated. Emissivity is the difference between ideal black body radiation and the measured object. Emissivity is greatly affected by the film stack thickness and composition.

The reactor used in this study has two types of wafer temperature measurement systems, Aixtron ARGUS and Laytec EpiTT. ARGUS uses an array of diodes to map the whole wafer as the wafer rotates. The diode array measures the wafer emission on two wavelengths. On the other hand, EpiTT provides emissivity corrected temperature on certain locations with the same radius on the wafer. The measurement is based on the CCD array approach. In addition, a LED light source is used to measure the wafer reflectivity spectrum in the infra-red for the emissivity correction. An optical fibre is connected between the reactor showerhead and the instrument. In principle, emissivity corrected wafer temperature mapping is possible. However, it could prove difficult to connect multiple CCD array based instruments to the reactor. In practice, the EpiTT is used to ascertain the growth temperature. On the other hand, ARGUS is employed to adjust heater balance for uniform wafer temperature profile.

Stable and uniform wafer surface temperature is vital in delicate growth steps. For instance, indium incorporation in InGaN quantum well formation for LEDs is extremely sensitive to growth temperature. In addition, uniform radial temperature profile can help to minimize wafer bow and film stresses during growth.

Additional information can be extracted when multiple in situ measurements are combined. For example, the temperature gradient of the substrate or the layer composition can be estimated [35]. The composition analysis requires information on the wafer surface temperature, wafer curvature and layer thickness. The change of curvature as a function of layer thickness can be used to assess the lattice mismatch between the substrate and the epitaxial layer. The lattice mismatch can be then in turn used to estimate the composition of the epitaxial layer. In addition, deviation from linear relation between thickness and curvature can be seen as a change in the material quality. For example, a transition to a different curvature slope might indicate the onset of plastic deformation or relaxation of the epitaxial layer [35]. Therefore, critical thickness for certain films could be obtained.

# 5 Characterization methods

Characterization is required in order to assess material quality and properties. The results can be then in turn used to optimize growth parameters. Modern MOVPE reactors offer some in situ monitoring. However, wafer mapping or more delicate measurements, such as x-ray diffraction, cannot be conducted during growth. In this chapter, optical epitaxial layer thickness measurement with spectrophotometer, x-ray diffraction and wafer geometry measurements are discussed. These measurements provide insight about the epitaxial growth uniformity, material quality (dislocations), wafer strain and bow. Other typical measurements are photoluminescence for quantum well uniformity assessment and Hall measurement for electrical properties such as mobility.

# 5.1 Spectrophotometer

Spectrophotometer is a measurement tool for optical characterization of thin film structures. The tool employs normal incident white light spectroscopy to simultaneously estimate film thickness and optical properties. A simple one layer model for white light reflection gives a thickness estimate

$$t = \frac{N}{2n(\frac{1}{\lambda_1} - \frac{1}{\lambda_2})},\tag{12}$$

where t, N, n,  $\lambda_1$  and  $\lambda_2$  are thickness, number of oscillations between two reflection maximums, refractive index of the film and the wavelengths of the maxima, respectively.

For more accurate measurements, wavelength dependent refractive index and absorption coefficient together with multiple layers are employed [36]. Absolute reflectivity can be resolved by comparing the sample reflectance spectrum to a know reference. A simulated reflectance is fitted to the experimental curve to extract material parameters.

In this work, the GaN on Si structure was modelled as a two layer system in order to measure the film thickness. It should be noted that the film stack consists of an AlN layer, an AlGaN graded buffer and two GaN layers. The measurement software provided a table of the refractive index for the silicon substrate as a function of wavelength. The epitaxial layers were modelled with a two coupled Lorentz oscillator model, the dielectric constant [36]

$$\epsilon(E) = \epsilon_{\infty} \left(1 + \sum_{j=1}^{2} \frac{A_j^2}{(E_{center})_j^2 - E(E - iv)}\right),\tag{13}$$

where  $\epsilon_{\infty}$ ,  $E_{center}$ ,  $A_j$  and v are the high frequency lattice dielectric constant, the center energy of each oscillator, the amplitude (strength) of each oscillator and the electron scattering frequency, respectively. Table 2 presents the parameters used in the model. The coupled model is a generalization of the standard Lorentz oscillator model. In the standard model, the oscillators are independent.

| Table 2. I arameters used in the coupled Lorentz oscillator model. |                     |                  |           |        |                |  |

|--------------------------------------------------------------------|---------------------|------------------|-----------|--------|----------------|--|

| Oscillator                                                         | $\epsilon_{\infty}$ | $E_{center}(eV)$ | $A_j(eV)$ | v(eV)  | coupling coef. |  |

| 1                                                                  | 3.278               | 5.716            | 3.605     | 0.2826 | 2.874          |  |

| 2                                                                  | 3.278               | 4.226            | 1.325     | 0.8025 | -              |  |

Table 2: Parameters used in the coupled Lorentz oscillator model.

Despite the fact that the film stack was modelled with a two layer system, the tool produced accurate measurements. The results were confirmed by imaging a cross-sectional sample of the epitaxial layers with scanning electron microscope.

# 5.2 X-ray diffraction

X-ray radiation is electromagnetic radiation with wavelengths between gamma rays and ultraviolet light. Typically, x-rays are generated by bombarding a metal with electrons in a vacuum tube. X-rays can be used to study the material lattice as the x-ray wavelength is comparable to the atomic spacing enabling x-ray diffraction (XRD) measurements [37]. Compared to electron microscopy or atomic force microscopy, the x-ray based characterization has a larger probe size. The diffraction based method sees the collective effect of crystal quality whereas the microscopes can see only individual defects.

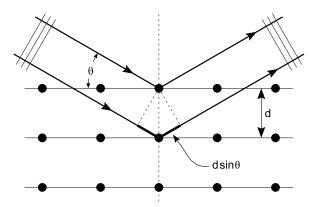

The wavelength in diffraction studies is in the order of 0.1 nm. The crystal lattice can be seen as a diffraction grating. Constructive interference occurs when the path difference from the lattice planes is equal to an integer multiple of wavelength. The constructive interference is described by the Bragg's law

$$n\lambda = 2dsin\theta,\tag{14}$$

where n,  $\lambda$ , d, and  $\theta$  are the order of diffraction, wavelength, distance between the lattice planes and angle of diffraction, respectively. Figure 16 presents the Bragg's law geometrically. In practice, n is chosen to be one. This can be done by using specific lattice planes. The distance between the planes can be altered by using a subset of lattice plane group, for example, taking every other lattice plane. For a

Figure 16: Geometrical representation of the Bragg's law [38].

hexagonal lattice, the plane spacing is [39]

$$d = \sqrt{\frac{3}{4(\frac{h^2 + k^2 + hk}{a^2} + \frac{3l^2}{4c^2})}},\tag{15}$$

where h, k and l are the Miller indices of the plane and a and c are the lattice constants.

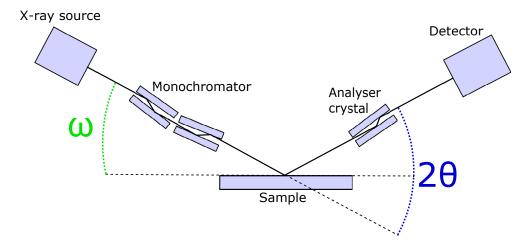

Figure 17 presents a typical high resolution x-ray diffraction (HRXRD) -setup. The output beam of a x-ray source is directed to a monochromator. The monochromator is used to select ideally a single wavelength from the beam and, on the other hand, make the beam narrow. The monochromator is based on quadruple diffration from nearly perfect germanium crystals [15]. This increases the the resolution of the setup as the Bragg's condition is satisfied at smaller range. The incident beam angle from the sample surface is called  $\omega$ . The sample diffracts the incoming beam. The angle between the diffracted beam and the incident beam is called  $2\theta$ . The diffracted beam is then directed to a detector through an analyser crystal. Similar to the monochromator, the analyser increases the measurement resolution. The analyser employs three diffraction events. Thus, the acceptance angle to the detector is reduced. However, when using the monochromator and the analyser the measured intensity drops. As as result, HRXRD measurements are typically slower than conventional XRD measurements. Therefore, the setup choice is a compromise between time and precision.

Figure 17: Schematic diagram of high resolution XRD setup.

The concept of reciprocal space is convenient when processing diffractions from lattice planes. Reciprocal lattice can be constructed from the basis vectors of three dimensional lattice. If the direct space lattice vectors are  $\mathbf{a}_1, \mathbf{a}_2$  and  $\mathbf{a}_3$ , the reciprocal

space vectors are defined as

$$\mathbf{b}_{1} = \frac{\mathbf{a}_{2} \times \mathbf{a}_{3}}{\mathbf{a}_{1} \cdot \mathbf{a}_{2} \times \mathbf{a}_{3}},$$

$$\mathbf{b}_{2} = \frac{\mathbf{a}_{1} \times \mathbf{a}_{3}}{\mathbf{a}_{1} \cdot \mathbf{a}_{2} \times \mathbf{a}_{3}} \text{ and}$$

$$\mathbf{b}_{3} = \frac{\mathbf{a}_{1} \times \mathbf{a}_{2}}{\mathbf{a}_{1} \cdot \mathbf{a}_{2} \times \mathbf{a}_{3}}.$$

$$(16)$$

It can be seen that the cross product in equations 16 causes the reciprocal lattice vector to be perpendicular to the respective real space vectors. In addition, the denominator of the equations is the volume of the real space unit cell. Therefore, reciprocal lattice unit cell volume is the reciprocal of the real space volume. These properties lead to the usefulness of the reciprocal space. It turns out that if a vector  $\mathbf{H}_{hkl}$  is drawn in the reciprocal space from the origin to coordinates (h,k,l), the vector is perpendicular to the real space lattice plane with Miller indices (hkl). The length of the vector  $\mathbf{H}_{hkl}$  is related to the plane distance in real space,  $|\mathbf{H}_{hkl}| = 1/d_{hkl}$ . Furthermore the vector  $\mathbf{H}_{hkl}$  is related to the wave vectors of the incident and scattered beam,  $\mathbf{H}_{hkl} = \mathbf{k}_0 - \mathbf{k}_s$ . [15]

Two type of measurements are typically conducted when characterising semiconductor samples [37]. These are the  $\omega$  and the  $\omega-2\theta$  scans. The  $\omega-2\theta$  scan can be seen as changing the length of the scattering vector in reciprocal space while maintaining the direction. The ratio between the angles is maintained, that is,  $\omega=2\theta/2$ . This essentially means that lattice planes of the same orientation but with different spacing are probed. Individual peaks around a certain reciprocal lattice point are typically created by different materials in the sample. Peak broadening on the other hand is mostly caused by the variation in the lattice spacing. The  $\omega$  scan, on the other hand, traces an arc around the origin of reciprocal space. The scattering vector length is maintained but the direction is changed. This can be interpreted as probing lattice planes with the same spacing but with different orientation. The peak broadening can be related to material quality.

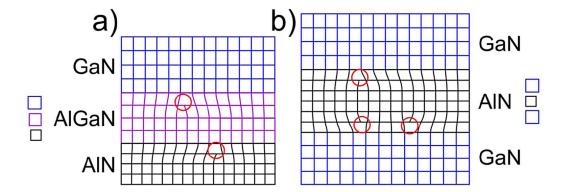

Reciprocal space maps are 2D slices of the reciprocal space. Typically, multiple  $\omega$  scans are conducted with different  $\omega - 2\theta$  values. Reciprocal space maps are especially useful for characterising strained layers. The reflection peaks in these samples can have considerable  $\omega$  offsets. The individual layer quality can be estimated based on the  $\omega$  and  $\omega - 2\theta$  peak broadening. In the reciprocal space, these are the  $Q_x$  and  $Q_y$  coordinates. The relaxation between the layers can be seen in the separation of the peak maxima in  $\omega$ -axis. Similarly, relaxation can be seen in the peak separation in terms of the  $Q_x$  coordinate. The incident and scattered beam angles can be translated to reciprocal spaces using the equations [40]

$$Q_x = \frac{1}{2}(\cos(\omega) - \cos(2\theta - \omega)) \text{ and}$$

(17)

$$Q_y = \frac{1}{2}(\sin(\omega) + \sin(2\theta - \omega)). \tag{18}$$

The structure of a highly non-ideal crystal film is typically approximated with the mosaic model [41]. It should be noted that for lower defect densities other models should be employed [37]. The mosaic model assumes that the film consists of ideal grains that are slightly misoriented with each other. The misorientation is divided into two orthogonal components. Rotation around the axis perpendicular to substrate surface is called twist and rotation parallel to substrate is called tilt. At the grain boundaries, tilt creates edge dislocations. On the other hand, twist causes screw dislocations.

The assessment of material quality based on XRD measurements is not trivial. Although the broadening of diffraction peaks can be related to material quality, there is a plethora of other factors. In addition, the choice of the defect model has a considerable effect on the estimates produced. However, XRD measurements are typically employed to assess a sample series quantitatively. Then one can assume that most of the differences are caused by the samples and less by the measurement setup. The qualitative analysis, for example, between different research groups, is considered somewhat unreliable. The XRD line shapes can be affected by dislocations, strain, wafer curvature, thickness variation, composition variation, limited sample size and measurement setup [37]. However, for high dislocation density samples, the effect of material quality dominates. This is usually the case for GaN layers on silicon substrates. In addition, some of the effects can be separated by taking scans from different diffraction planes [37,42].

# 5.3 Wafer geometry measurement

Wafer geometry measurements are conducted to assess the strain of the epitaxial layers after growth. In addition, wafer bow is crucial as too high bow can prohibit post processing. Non-contact measurement is usually required in order to limit wafer contamination.

In this study, a non-contact wafer geometry measurement was used. The measurement is based on capacitance change. A capacitance probe is brought to close proximity to the wafer. The capacitance between the wafer surface and the probe as a function of distance is known [43]. The measured capacitance is compared to a capacitance of a known reference. Thus, the distance can be calculated.

There are probes on either side of the wafer. When the distances between the probes and the wafer are measured, the wafer thickness can also be estimated. The wafer is scanned with the probes and, thus, the wafer geometry can be resolved.

The probes employ a so called push-pull scheme. A probe contains two terminals and an AC current is run between the terminals. This configuration limits the effect of varying wafer conductivity on the measurement [43].

### 6 Gallium nitride on silicon

Epitaxy of GaN on Si is challenging because of the vastly different material properties. Firstly, the lattice mismatch of c-plane GaN and (111) Si is 17% [2]. Second reason is the 46% difference in the thermal expansion coefficients between the two [2]. Moreover, GaN cannot be directly grown on silicon because gallium reacts aggressively with silicon causing a phenomenon called meltback etching [5]. Despite these challenges, (opto)electronic grade GaN can be realized on silicon substrates. Considerable amount of research has been directed to match GaN and Si [5]. Indeed, multiple seed and buffer layer schemes have been proposed [5].

From the device perspective, the high resistivity of Al containing layers and, on the other hand, Si substrate conductivity and low breakdown field place limitations [5]. Moreover, in optical applications, the Si substrate absorbs considerable amount of GaN emitted light. Therefore, the silicon substrate has to be removed [23]. Nevertheless, commercial GaN on Si blue LEDs are available [23].

#### 6.1 Substrate orientation